FPGA

See artikkel ootab keeletoimetamist. |

FPGA (field-programmable gate array, kohapeal programmeeritav väravamassiiv või programmeeritav ventiilmaatriks[viide?]) on integraallülitus, mille tootja on disaininud nii, et selle lülituse täpse konfiguratsiooni saab määrata ehk programmeerida kasutaja.

Arhitektuur

[muuda | muuda lähteteksti]FPGA koosneb programmeeritavatest loogikakomponentidest, mida kutsutakse loogikaplokkideks, ja seadistatavatest vaheühendustest, mille abil saab loogikaplokke ühendada. Loogika plokke saab panna tegema keerulisi funktsioone aga ka lihtsaid loogilisi tehteid nagu näiteks AND ja XOR. Sageli on FPGA loogikaplokkides ka mäluelemendid, mis võivad olla lihtsad trigerid või keerulisemad mäluüksused.[1]

Lisaks digitaalsetele funktsioonidele on mõnel FPGA-l võimalused ka analoogelektroonika jaoks. Enamasti saab programmiliselt muuta kiibi jalal oleva signaali muutumise kiirust ja väljundvoolu tugevust. Sageli on kiipi integreeritud ka analoogsignaali komparaatoreid (võrdlejaid). Leidub ka seadmeid, milles on olemas nii analoog-digitaalmuundurid kui ka digitaal-analoogmuundurid, mis lubavad FPGA-l käituda nagu süsteemikiip.[2]

Kõige levinum FPGA arhitektuur[1] koosneb loogikaplokkide massiivist (sõltuvalt tootjast kutsutakse seda kas seadistavaks loogikaplokiks (CLB) või loogika-massiiviplokkiks (LAB)), sisend/väljund jalgadest ning vaheühendustest. Üldiselt on kõigil ühendustel sama ribalaius.

Rakenduse mikrokiip peab olema FPGA-le tõlgendatud adekvaatsete ressurssidega. Kui CBL/LAB-de ja sisendite/väljundite arvu saab kergesti tuletada konkreetsest disainist, siis ühendusradade arv võib isegi sama palju loogikat sisaldavate skeemide puhul märgatavalt varieeruda. Kuna kasutamata ühendusrajad lisavad hinda, aga mitte tulemust, siis üritavad FPGA-de tootjad pakkuda just piisavalt radasid, et enamikku disainivariantidest, mis sobivad loogika elementide arvu poolest, oleks võimalik ühendada. Need arvud on saadud hinnangute, mis on tuletatud Renti reeglist, või olemasolevate disainidega eksperimenteerimise abil.

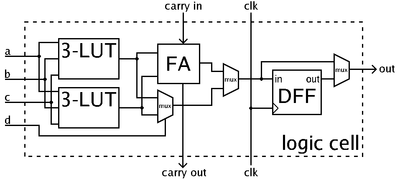

Loogikarakud loogikaplokis

[muuda | muuda lähteteksti]Üldiselt koosneb loogikaplokk (CLB või LAB) mõnest loogikarakust. Tüüpiline loogikarakk koosneb 4 sisendiga otsingutabelist, täisliitjast ja D-tüüpi flip-flopist nagu all näidatud. Otsingutabel on joonisel jagatud kaheks 3 sisendiga otsingutabeliks. Tavarežiimis on need läbi vasakul oleva multipleksori kombineeritud üheks 4 sisendiga otsingutabeliks. Aritmeetikarežiimis söödetakse nende väljundid liitjale. Režiimi saab valida keskmise multipleksori programmeerimise abil. Väljund võib olla sünkroonne või asünkroonne sõltuvalt joonisel paremal asuva multipleksori programmeerimisest. Praktikas kasutatakse tervet või osa täisliitjast otsingutabeli funktsioonina, et ruumi säästa.[3][4][5]

Loogikarakk koosneb tavaliselt kahest või neljast sellisest struktuurist, kus mõned signaalid on neile ühised. Loogikaplokkides on tüüpiliselt omakorda mõned loogikarakud.

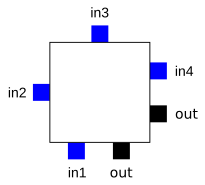

Viimastel aastatel on tootjad oma tippklassi toodetes asendanud 4 sisendiga otsingutabelid 6 sisendiga otsingutabelite vastu, mis pidid kiiremad olema.[6] Kuna kella signaali jaoks on tavaliselt kasutusel eraldi rajad, siis tegeletakse nende signaalidega eraldi. Selle näidisarhitektuuri loogikaploki jalgade asukoht on näidatud alloleval joonisel.

Iga sisend on juurdepääsetav ühest loogikaploki küljest, samal ajal kui väljund võib minna ainult kas paremal või all asuvale loogikaplokkide kanalile. Iga väljund võib olla ühendatud naaberloogikaploki suvalise sisendi külge.

Sarnaselt võib sisend/väljund jalg olla ühendatud suvalise ühenduse segmendiga, mis asub naaberkanalil. Näiteks kiibi ülal paikneva sisend/väljund jala võib ühendada suvalise juhtmega, mis asub tema all paikneval horisontaalsel kanalil.

Üldiselt on FPGA vaheühendused segmenteerimata. See tähendab, et iga ühenduse osa ulatub ühe loogikaplokini ja lõppeb lülitikarbis. Mõnede programmeeritavate lülitite sisselülitamine lülitikarbis tekitab pika pikema raja. Kiiremate vaheühenduste saavutamiseks kasutavad mõned FPGA arhitektuurid ka pikemaid radasid, mis läbivad mitut loogikaplokki, enne kui jõuavad mõnda lülitikarpi.

Kõikjal, kus ristuvad vertikaalne ja horisontaalne loogikaplokkide kanal, on lülitikarp. Sellises arhitektuuris, kus rada läheb lülitikarpi, on kolm programmeeritavat lülitit, mis määravad ära, millise teise samasse karpi mineva rajaga see rada ühendatakse.

Moodsas FPGA-s võib lisaks olla veel kõrgema taseme funktsionaalsust, mis on riistvaraliselt fikseeritud. Üldkasutatavate funktsioonide fikseerimine vähendab vajaminevat pindala ja teeb need kiiremaks võrreldes primitiivsetest loogikaplokkidest tehtutega. Sellistest lisaelementidest on kõige sagedasemad: kordajad, integreeritud protsessorid, kõrge kiirusega sisend/väljund loogika ja sisseehitatud mälu.

FPGA-sid kasutatakse laialdaselt ka süsteemidisaini testimiseks. See lubab mikrokiibi valmistajatel testida oma disaini enne, kui mikrokiip tehases valmis tehakse.

FPGA arhitektuuri võrdlus teiste sarnaste lahendustega

[muuda | muuda lähteteksti]Teadusuuringutes[7] on näidatud, et FPGA-del teostatud elektroonikalülitused võtavad keskmiselt umbes 18 korda rohkem pindala, vajavad 7 korda rohkem elektrivoolu ja on 3 korda aeglasemad kui samad lahendused rakendusespetsiifilise integraallülituse (ASIC) peal.

FPGA eelisteks on paindlikkus – võimalus skeemi vigade parandamiseks lülitust uuesti seadistada ehk programmeerida. Tavaliselt läheb FPGA-del juurutatud toote turule toomiseks vähem aega.[8]

Tootjad saavad valida ka kesktee, kui nad arendavad välja oma toote disaini FPGA peal, kuid lõppversiooni toodavad tavalise tehnoloogia baasil.

Võrdlus keerukate programmeeritavate loogikaseadmetega CPLD

[muuda | muuda lähteteksti]Peamised erinevused kompleksse programmeeritava loogikaseadme (CPLD) ja FPGA vahel on arhitektuuriline. Loogikaseadmetel on tavaliselt väike hulk loogikaväravate jadasid, mis hiljem kokku kogutakse, ja nii saab täpsemini ennustada aega, mis kulub signaali töötlemiseks. Lisaks saab neile paigutada rohkem loogikat, aga vähem loogikaelementide vahelisi ühendusi, mis tähendab omakorda vähem paindlikkust. FPGA arhitektuuris on just nimelt loogikaplokkide vahelistel ühendustel rohkem rõhku ja see muudab nad paindlikumaks.

Ajalugu

[muuda | muuda lähteteksti]Valmimine

[muuda | muuda lähteteksti]FPGA kasvas välja programmeeritavatest püsimäludest (PROM) ja programmeeritavatest loogikaseadmetest (PLD). Neid mõlemaid sai programmeerida, aga loogikaväravate-vahelised ühendused jäid samaks.[9]

Ameerika Ühendriikide Merepinna Sõjandusdepartemang (Naval Surface Warfare Department) rahastas hilistel 1980ndatel Steve Casselman juhitud eksperimenti, mille eesmärgiks oli luua arvuti, mis juurutaks 600 000 taasprogrammeeritavat loogikaväravat. Casselmanil see õnnestus ja sellega seonduv patent anti välja 1992. aastal.

Mõned teedrajavad kontseptsioonid ja tehnoloogiad programmeeritavate loogikaväravate ja loogikaplokkide kohta leiduvad patentides, mis anti 1985. aastal David W. Page'ile ja LuVerne R. Petersonile.

Xilinxi kaasasutajad Ross Freeman ja Bernard Vonderschmitt leiutasid 1985. aastal esimese kommerts-FPGA – XC2064.[10] XC2064-l olid programmeeritavad väravad ja programmeeritavad vaheühendused. See oli uue tehnoloogia ja turu algus.[11] XC2064-l oli 64 seadistatavat loogikaplokki, millel oli kaks 3 sisendiga otsingutabelit.[12]

Xilinx jätkas konkurentideta ja kasvas kiirelt kuni 1990. aastate keskpaigani, millal konkurendid kanda kinnitasid. 1993. aastaks oli Acteli käes 18% kogu FPGA-de turust.[11]

1990. aastad oli FPGA-de jaoks kiire kasvu periood nii keerukuse kui ka tootmismahtude poolest. 1990. aastate alguses kasutati FPGA-sid peamiselt telekommunikatsioonis ja võrgusides. Kümnendi lõpuks leidsid FPGA-d tee tööstuslikesse rakendustesse.[13]

Areng tänapäeval

[muuda | muuda lähteteksti]Hiljutine trend on viia traditsiooniline FPGA edasi ja ühendada see mikroprotsessori ja teiste lisaseadmetega, et moodustada süsteemikiip. Näiteks sellistest hübriidtehnoloogiatest võib tuua Xilinx Virtex-II PRO ja Virtex-4 seadmed, kus on üks või rohkem PowerPC protsessorit FPGA loogikakangasse integreeritud. Atmeli FPSLIC on veel üks selline seade, mis kasutab AVR-i protsessorit koos Atmeli programmeeritava loogikaarhitektuuriga.

Alternatiivne lähenemine protsessorite kasutamises on võimalus kasutada tarkvaralisi protsessoreid, mis on juurutatud otse FPGA loogikale.

Lisaks hakkavad tekkima mõned uued arhitektuurid, mis ei ole enam tüüpilised FPGA-d. Tarkvaraliselt seadistatav mikroprotsessori seeria Stretch S5000 kasutab hübriidset lähenemist, pakkudes kasutajale tavalisi protsessorituumasid ja FPGA-sarnaseid programmeeritavaid tuumasid samal kiibil.

Loogikaväravate arvu kasv

[muuda | muuda lähteteksti]- 1987: 9000, Xilinx[11]

- 1992: 600 000, Naval Surface Warfare Department

- ~2000: miljonid[13]

- 2010: miljardid

Turu areng

[muuda | muuda lähteteksti]- 1985: esimene kommerts-FPGA-tehnoloogia leiutati Xilinxi poolt.[11]

- 1987: 14 miljonit dollarit[11]

- ~1993: üle 385 miljoni dollari[11]

- 2005: 1,9 miljardit dollarit[14]

- 2010: hinnanguliselt 2,75 miljardit dollarit[14]

Rakendused

[muuda | muuda lähteteksti]FPGA rakenduste seas on signaalitöötlus, tarkvaraline raadio, rakendusespetsiifilise mikroskeemi prototüüpimine, pilditöötlus, kõnetuvastus, krüptograafia, bioinformaatika, arvutiriistvara emuleerimine, raadioastronoomia ja kasvav hulk igasugu muid rakendusi.

FPGA-d alustasid pakkudes alternatiivi komplekssetele loogikaseadmetele. Nende ülesandeks oli teiste laialdaselt levinud skeemide ühendamine. Kui FPGA-de võimalused kasvasid, hakkasid nad järjest rohkem ülesandeid täitma. Tänapäeval on mõned kohe päris süsteemikiibi rollis.[15][16]

FPGA-d leiavad eriti kasutust just seal, kus osatakse ära kasutada nende arhitektuuri pakutavat paralleelsust. Üheks selliseks alaks on koodimurdmine ja krüptograafiliste algoritmide lahendamine jõumeetodil.

FPGA-d kasutatakse ka muidu palju tehteid nõudvate algoritmide kiirendamiseks, et säästa protsessoriressurssi (sageli on pudelikaelaks just andmevahetuskiirus ja seetõttu sobib FPGA-le anda ülesandeid, kus on vaja samade andmetega teha palju tehteid). FPGA-d pole veel saanud iga kõrgema otsa arvuti osaks, sest nende programmeerimine on võrreldes tavalise tarkvaraga kordades keerulisem ja selleks ei ole veel piisavalt häid tööriistu, mis suudaksid seda keerukust vähendada.

Traditsiooniliselt on FPGA-sid kasutatud peamiselt väikesemahulistes projektides. Väikeste mahtude juures on FPGA-de eest makstav lisaraha siiski väiksem, kui rakendusespetsiifilise mikroskeemi tootmine. Tänapäeval on langenud hinnad ja kasvanud jõudlus oluliselt laiendanud FPGA-de tööpõldu.

Seadistamise eripärad

[muuda | muuda lähteteksti]FPGA konfiguratsioon määratakse tavaliselt riistvara kirjeldamise keelega (hardware description language – HDL). See kirjeldus sarnaneb sellise keele kirjeldusega, millega kirjeldatakse rakendusespetsiifilisi integraallülitusi (application-specific integrated circuit – ASIC). FPGA abil on võimalik teostada iga loogilist funktsiooni, mis rakendusspetsiifilises integraallülituses võib eksisteerida.[17]

Et määrata FPGA käitumine, peab kasutajal olema riistvara kirjeldamise keelega (hardware description language – HDL) või elektriskeemiga disain. HDL on parem vorm, kui on vaja töötada suurte struktuuridega, sest seal saab neid nummerdada, mitte ei pea igat väikest osa käsitsi joonistama. Aga visualiseerimiseks on parem kasutada skeemi.

Kasutades seejärel mõnda abiprogrammi, genereeritakse elektriliste ühenduste nimekiri. Seejärel saab selle ühenduste nimekirja konkreetse FPGA peale kaardistada. Selle jaoks on tavaliselt FPGA tootja valmistatud kinnine tarkvara. Kasutaja vaatab tulemuse üle erinevate valideerimismeetoditega, mis võivad näidata nii ajastuse analüüsi kui ka süsteemi simulatsiooni.

Kui disainimise ja valideerimise protsess on lõppenud, genereeritakse FPGA tootja tarkvara poolt binaarfail, mille abil seadistatakse lõpuks FPGA. Seadistamiseks kasutatakse jadaühendust või välist mäluseadet.

Kõige tavalisemad HDL-id on VHDL ja Verilog. Kuid HDL-id on tavaliselt suhteliselt keerulised ja seda võrreldakse oma raskusastme poolest assemblerkeelega.

Et lihtsustada komplekssete süsteemide disainimist FPGA-del, on loodud teeke, mis sisaldavad keerulisi funktsioone ja skeeme, mis on testitud ja optimeeritud. Inglise keeles on nende nimetus tihti "IP cores" ja nad on saadaval FPGA-de tootjate ja kolmandate osapoolte käest. Enamasti on need tasulised ja kinniste litsentsidega, kuid mõned on ka avatud lähtekoodi ja vaba litsentsiga.

Vaata ka

[muuda | muuda lähteteksti]- Peamised riisvara kirjeldamise keeled:

- Loogikaväravate massiiv

- Programmeeritav süsteemikiip

- rakendusespetsiifiline mikroskeem (Application-specific integrated circuit e ASIC)

- kombinatoorne loogika

- kompleksne programmeeritav loogikaseade (CPLD)

- tarkvaraline protsessor

Viited

[muuda | muuda lähteteksti]- ↑ 1,0 1,1 FPGA Architecture for the Challenge

- ↑ Mike Thompson, EETimes Mixed-signal FPGAs provide GREEN POWER

- ↑ CycloneII Architecture

- ↑ Documentation: Stratix IV Devices

- ↑ Virtex-4 FPGA User Guide

- ↑ "Achieving Higher System Performance with the Virtex-5 Family of FPGAs" (PDF). Originaali (PDF) arhiivikoopia seisuga 27. september 2007. Vaadatud 14. detsembril 2010.

- ↑ http://doi.acm.org/10.1145/1117201.1117205

- ↑ Tim Erjavec, White Paper, "Introducing the Xilinx Targeted Design Platform: Fulfilling the Programmable Imperative."

- ↑ "History of the programmable logic". Originaali arhiivikoopia seisuga 23. jaanuar 2013. Vaadatud 23. jaanuaril 2013.

- ↑ Peter Clarke, EE Times, "Xilinx, ASIC Vendors Talk Licensing."

- ↑ 11,0 11,1 11,2 11,3 11,4 11,5 Funding Universe. "Xilinx, Inc."

- ↑ Clive Maxfield, Programmable Logic DesignLine, "Xilinx unveil revolutionary 65nm FPGA architecture: the Virtex-5 family.

- ↑ 13,0 13,1 Clive Maxfield, raamat "The Design Warrior's Guide to FPGAs". Kirjastas Elsevier, 2004. ISBN 0750676043, 9780750676045.

- ↑ 14,0 14,1 Dylan McGrath, EE Times, "FPGA Market to Pass $2.7 Billion by '10, In-Stat Says".

- ↑ FPGA/DSP Blend Tackles Telecom Apps

- ↑ Mark LaPedus, EETimes Xilinx aims 65-nm FPGAs at DSP applications

- ↑ Wiśniewski, Remigiusz (2009). Synthesis of compositional microprogram control units for programmable devices. Zielona Góra: University of Zielona Góra. Lk 153. ISBN 978-83-7481-293-1.