RISC

| See artikkel räägib mikroprotsessorist; RISC nimetuse all on tuntud ka RNA-indutseeritud geenivaigistamiskompleks. |

See artikkel ootab keeletoimetamist. |

See artikkel vajab ajakohastamist. (Juuli 2021) |

Kärbitud käsustikuga arvuti (ingl reduced instruction set computer, RISC) on mikroprotsessor, mis on välja töötatud nii, et see saavutab suurema töökiiruse läbi täidetavate käskude arvu minimeerimise. Käskude täitmise kiirust mõõdetakse selle järgi, et mitu miljonit operatsiooni sekundis suudab arvuti sooritada (MIPS – millions of instructions per second). Seda põhjusel, et iga lisanduv käsutüüp nõuab rohkem transistoreid ning suuremat ja keerulisemat protsessorit. Suurem hulk käsutüüpe ja käske tähendab paratamatult suuremat, keerukamat, aeglasemat ja ka kallimat mikroprotsessorit.

Sõna "kärbitud" (reduced) ei viita siin tarbetute käskude kustutamisele, vaid ühe käsu täitmise kiirendamisele. Kõige tavalisemalt teostatakse see ühe suure ja mahuka operatsiooni jagamisega mitmeks osaks (RISC protsessori puhul neljaks) ja iga taktiga täidetakse üks operatsioon. See erineb CISC-protsessorist, kus mahukas operatsioon sooritatakse tervikuna korraga.

Ajalugu

[muuda | muuda lähteteksti]RISC-i põhiprintsiip sai alguse 1974. aastal, kui John Cocke IBM-i Yorktownis asuvast teadusasutusest tõestas, et 20% käskudest sooritasid 80% arvuti tööst. Esimene RISC arvuti loodi juba kümme aastat enne termini välja mõtlemist. CDC 6600 superarvuti, mis põhines 'lae/salvesta arhitektuuril', mida on ka alternatiivina pakutud RISC arhitektuuri nime asemel. 1975. aastal alustas IBM tööd esimese RISC protsessori väljaarendamiseks, mille tulemusel loodi IBM 801 protsessorite seeria.

Arvutite kiiremaks muutumisele aitas RISC-tehnoloogia kaasa sellega, et protsessori käskudele tehti kvantitatiivne analüüs ning harva vajaminevad käsud eemaldati protsessori käsustikust ja emuleeriti tarkvaraliselt. Selle eelised on:

- Kiibis tühjaks jäänud "ala" saab kasutada enamkasutatavate käskude kiirendamiseks; see annab suurema kiiruse isegi koos tarkvaras emuleeritud käskude täitmise suurema ajakuluga.

- Protsessori disaini optimeerimine muutus lihtsamaks.

- See lubab protsessoritel kasutada tehnikaid, mis varem olid võimatud.

- Lihtsustab tõlkimist kõrgematest programmeerimiskeeltest – kiiremad programmid.

RISC-arhitektuuri algusaastatel tehti ka ainult RISC-käsustikul põhinevaid süsteeme, näiteks: DEC Alpha, AMD 29k, ARC, ARM, Atmel AVR, Blackfin, MIPS, PA-RISC, Power (s.h PowerPC), SuperH, ja SPARC.

CISC ja RISC

[muuda | muuda lähteteksti]Käskude kodeerimise viisi järgi saab protsessoreid liigitada järgmiselt:

- CISC (Complex Instruction Set Computer) – selline protsessor võib ühe käsu raames teha mitu mikrooperatsiooni. CISC-protsessorile kirjutatud programmid on mahult väiksemad, lisaks on neid masinkoodis ka suhteliselt lihtne kirjutada.[viide?]

- RISC (Reduced Instruction Set Computer) – protsessor töötab üksnes võimalikult lihtsate mikrooperatsioonidega. RISC-protsessorile kirjutatud programmid vajavad rohkem mälu, sest kõik mikrooperatsioonid tuleb eraldi kirja panna. Ühtlasi on selliseid programme masinkoodis ka raskem kirjutada kui CISC programme. RISC-protsessor saab käskude täitmisega kiiremini hakkama, kuna ei pea erinevalt CISC-protsessorist mikrokoodi teisendama.

| RISC | CISC |

|---|---|

| Lihtsam käsustik | Palju keerukaid käske |

| Vähem käske | Erineva pikkusega käsud |

| Kindla pikkusega käsud | Keeruline mikrokood |

| Keeruline kompileerija | Paljud käsud pääsevad ligi mälule |

| Ainult 'Laadi/salvesta' käsud pääsevad ligi mälule | Palju adresseerimisviise |

| Vähe adresseerimisviise |

CISC tüüpi protsessorid on sama kiired kui RISC tüüpi protsessorid. Kui arvestada energiakulu (MIPS/W), on RISC tüübi protsessori jõudlus ühe vati kohta suurem kui CISC tüüpi protsessoril. Arvutite algusajal ei olnud olemas veel kompilaatoreid, kõik programmid tuli kirjutada otse masinkoodi või assembleri abil ja seetõttu oli lihtsam kirjutada programme CISC tüüpi protsessorile, sest protsessorile ei pidanud andma mikrokäsklusi, samas käskude arv CISC-protsessoris oli suurem.

RISC ja x86

[muuda | muuda lähteteksti]Vaatamata RISC-platvormi eelistele on domineerima jäänud Inteli x86 arhitektuur.

Selle peamised põhjused on järgmised:

- Enamik rakendusi on kirjutatud või kompileeritud x86 koodile, ühelgi RISC-arhitektuuril sellist standardset alust pole, ehk ARM-ile kirjutatud kood SPARC protsessoril ei jookse, x86 puhul taolist ühilduvuse probleemi ei ole.

- Kuigi RISC-protsessorid olid märkimisväärsete eelistega ja võrdlemisi odavad, oli Intelil selleks ajaks juba suur turuosa ja rohkem ressursse arenduseks. Cyrix-il ja AMD-l sellist võimalust ei olnud, kuid nad taipasid kasutada RISC-i pipeline'i ülesehitust ja kasutada seda x86 arhitektuuri puhul.

- Võimsamad x86 protsessorid, nt P6, Pentium 4 ning K6 ja K7, kasutasid dünaamilist puhverdamist ja ajastamise põhimõtteid ning realiseerisid mitme vaba mikrokoodi jada käivitamise, mis oli tehtud mitme paralleelse x86 dekodeerimise etapist.

Üks käsk tsükli kohta

[muuda | muuda lähteteksti]RISC-arvutite ülimaks sihiks oli üks käsk iga tsükli kohta (Clock Cycles per Instruction). Reaalsuses seda veel saavutatud pole, heaks saavutuseks peetakse juba 1,3 tsüklit, tavaline on aga 1,4...1,5 tsüklit ühe käsu jaoks. Soovitud tulemuse (CPI = 1) saaks saavutada juhul, kui kasutataks lõpmatu suuri vahemälusid ja pipeline'ides ei tekiks kunagi konflikte katkestuste ja hargnemiste tõttu.

Konveier

[muuda | muuda lähteteksti]

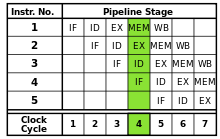

Iga RISC-süsteemi põhiomaduseks on konveier – see on viis, kuidas täita järjekorras olevaid käske paralleelselt. Joonisel on näide viieastmelisest konveierist. Iga konveieriaste täidab korraga ühte käsku.

- IF = käsu toomine (Instruction Fetch)

- ID = käsu avamine (Instruction Decode)

- EX = käsu käivitamine (Execute)

- MEM = mällu pöördumine (Memory access)

- WB = tulemuse kirjutamine registrifaili (Register writeback)

Mida rohkem on astmeid, seda suurem on paralleelsus ja seetõttu peaks suurem olema ka protsessori kiirus. Siiski vaid astmeid lisades hakkaksime kiiruse võitmise asemel hoopis kiiruses kaotama, kuna suurema arvu astmete korral tekib rohkem konflikte, mis omakorda nõuaksid keerulisemat riistvara.

Uuematel protsessoritel nagu kahetuumalisel ARM Cortex-A9-l on aga hoopis 8-astmeline konveier, kuid mõned protsessorid on kasutanud ka 12-astmelist konveierit. Kõige levinum on siiski näites toodud 5-astmeline konveier.

RISC-arhitektuuri omadused

[muuda | muuda lähteteksti]- 'Laadi/salvesta arhitektuur' (Load / Store Architecture) – ainult käskudel 'Laadi' ja 'Salvesta' on ligipääs mälule. Selle miinuseks on, et on vaja rohkem registreid, plussiks aga kiirem ligipääs andmetele programmi käivitamisel.

- Lihtsad adresseerimisviisid (Simple Addressing Modes) – kasutatakse vaid viit adresseerimisviisi, võrdluseks CISC puhul on neid üle 25. Tähtis on ka see, et need mahuksid olemasolevasse pipeline.

- Kindla suuruse ja väljaga käsud (Fixed size and fields instruction) – vajalik selleks, et oleks võimalik lugeda käsku ühe tsükliga, muidu kaoks pipeline'i mõte.

- Üks käsk tsükli kohta (One Instruction Per Cycle execution rate) – võimalik vaid pipeline'i kasutades.

- Harvardi arhitektuur – käskude ja andmete jaoks on eraldi vahemälu, see suurendab kiirust.

ARM

[muuda | muuda lähteteksti]Hetkel on enamik maailma protsessoritest RISC-tüüpi, näiteks ARM-i edasiarendatud (Advanced RISC Machines), tootis aastal 2005 98% miljardist müüdud mobiilitelefonide protsessoritest. ARM tähistas hiljuti ka 15 miljardi protsessori tootmist läbi aegade. ARM-i kiireim protsessor on praegu Cortex A-9, mis on saavutanud kiiruseks 2,5 GHz, oma mobiiltelefonidesse võime neid oodata 2013. aastaks. Hinnanguliselt toodetakse ainuüksi aastal 2011 5 miljardit ARM-i protsessorit. ARM-i tooted on kasutusel järgnevates seadmetes:

- Apple iPodid ja iPod Touch

- Apple iPhone

- Apple iPad ja iPad 2

- Palm ja PocketPC PDA-d ja nutitelefonid

- RIM BlackBerry nutitelefonid

- Microsoft Windows Mobile

- Nintendo Game Boy Advance

- Nintendo DS

- Sony Network Walkman

- Android nutitelefonid, tahvelarvutid

Paljud tootjad, sealhulgas HP Lenovo, Qualcomm jne. üritavad võita turuosa ARM protsessoritel põhinevate tahvelarvutite ja netbookidega, mis on varustatud kas mõne Linuxi distributsiooni või Androidiga.

Erinevad kasutusalad

[muuda | muuda lähteteksti]Oma lihtsuse, odavuse ja kiiruse tõttu on RISC protsessorid enamjaolt kasutatavad lihtsamates seadmetes: mobiiltelefonid, MP3-mängijad, mängukonsoolid jne. RISC-protsessoreid toodavad paljud erinevad tootjad, need on kasutusel nii PlayStationites, ruuterites kui ka Apple vanemates arvutites.

- MIPS seeria on leitav enamikest SGI, PlayStation, PlayStation 2, Nintendo64, PlayStation Portable mängukonsoolidest ning ruuteritest nagu Linksys WRT54G series.

- IBM-i ja Freescale Power Architecture kasutusel kõikides IBM-i superarvutites, serverites ja tööjaamades, lisaks tootis Apple veel mõned aastad tagasi PowerPC-baasil Macintoshe.

- Nintendo Gamecube ja Wii mängukonsool

- Microsofti Xbox 360 mängukonsool

- Sony's PlayStation 3 mängukonsool

- EMC's DMX Symmetrix SAN

- ja palju muud alates printeritest kuni autodeni.

- SPARC Oracle (endine Sun Microsystems) ja Fujitsu

- Hewlett-Packardi PA-RISC tuntud ka kui HP-PA, lõpetas December 31, 2008.

- Alpha kasutati lauaarvutites, tööjaamades, serverites ja superarvutites mis olid toodetud Digital Equipment Corporation, Compaq ja HP poolt, lõpetas alates 2007 aastast.

- XAP protsessor kasutusel paljudes madala voolutarbega traadita seadmete (Bluetooth, Wi-Fi) kiipides, mis olid toodetud CSR poolt.

- Hitachi SuperH kasutusel Sega Super 32X, Saturn ja Dreamcastis, nüüd südameks paljudele koduelektroonika seadmetele.

- Atmel AVR kasutusel paljudes erinevates kohtades Xboxi juhtseadmetest kuni BMW autodeni.

Välislingid

[muuda | muuda lähteteksti]- http://www.heyrick.co.uk/assembler/riscvcisc.html

- http://www.seas.upenn.edu/~palsetia/cit595s07/RISCvsCISC.pdf

- http://www.ece.ucdavis.edu/~vojin/CLASSES/EEC180B/Fall99/Writings/RISC-Chaptr.PDF

- http://search400.techtarget.com/definition/RISC

- http://encyclopedia2.thefreedictionary.com/RISC

- http://www.cs.washington.edu/homes/lazowska/cra/risc.html

- http://www.theinquirer.net/inquirer/news/2120734/arm-pitches-bit-armv8-architecture-server-vendors

- http://arm.com/files/downloads/Cortex-A9_Devcon_2007_Microarchitecture.pdf

- http://arstechnica.com/cpu/4q99/risc-cisc/rvc-6.html

- http://www.netbooknews.com/7887/arm-busts-out-28nm-cortex-a9-processor-reaches-2-5ghz/