Mikroarhitektuur

See artikkel ootab keeletoimetamist. (Juuli 2024) |

Mikroarhitektuur (inglise keeles microarchitecture), informaatikas ja arvutitehnikas kirjeldab mikroarhitektuur, kuidas protsessoris on teostatud etteantud käsustik. Kui käsustik kirjeldab, kuidas protsessor käske täidab, siis mikroarhitektuur kirjeldab, kuidas protsessori[1] osad on ühendatud loogiliselt ja füüsiliselt. Mikroarhitektuur võib kirjeldada ühendusi suuremate osade vahel, nagu kuidas aritmeetika-loogikaplokk on registritega ühenduses või kuidas on ühendatud individuaalsed loogikaväravad.

Mikroarhitektuuri ja käsustiku vahe

[muuda | muuda lähteteksti]Käsustik hoomab enda alla assemblerkeele, registrid, grammatika (syntax), käitumise (execution model), aadressid ja andmetüübid. Näiteks sama käsustiku jagavad kõik x86 protsessorid, x86_64 protsessorid (tuntud ka kui AMD64) ja muud teised.

Protsessori mikroarhitektuur on tavaliselt esitatud kui protsessori osade omavaheliste ühenduste loogikadiagramm. Nendel joonistel on tavaliselt eraldatud juhtsignaalid ja andmesignaalid. Mikroarhitektuuri erinevaid komponente on võimalik kirjeldada sarnaste skeemidega kus on näidatud ühendused erinevate loogika komponentide vahel, nendest loogika komponentidest on omakorda tehtud elektriskeemid mis kirjeldavad tema tööd[2].

Mikroarhitektuuri skeem koosneb aritmeetika-loogikaplokist, registritest, ühest või mitmest andmesiinist, puhvermälust, juhtliinidest. Diagramm näitab mis juhtsignaalide, sisendite ja väljunditega teatud masina osad tegelevad.

Erinevatel protsessoritel võivad olla erinevad lahendused, et saavutada sama lõpp tulemust kui teised sama käsustiku protsessorid. Mikroarhitektuuri muutused võivad esile tuua ka tehnoloogilised arengud kas pooljuhtides, tootmises või muus[3].

Sama mikroarhitektuuriga arvutitel on võimalik kasutada erinevaid käsustikke minimaalsete mikrokoodi muudatustega[4][5]. Mikrokood on protsessori sees olev püsimälu mis määrab kuidas protsessori masinkäske täidetakse. Uuematel protsessoritel on võimalik, et see püsimälu on ülekirjutatav (vaata välkmälu). Seda mikrokoodi uuendatakse tihti läbi BIOS ja UEFI püsivara uuenduste.

Mikroarhitektuuri mõisted

[muuda | muuda lähteteksti]Programmide käivitamiseks peab protsessori tegema järgmist:

- Mälust käsu lugemine.

- Käsu dekodeerimine

- Käsu täitmine

- Tulemuse salvestamine

Konveier ehk toru (pipeline)

[muuda | muuda lähteteksti] Pikemalt artiklis Toru (arvutustehnika)

Pikemalt artiklis Toru (arvutustehnika)

Konveier on kogum jadamisi ühendatud andmete töötlemise elemente, kus ühe elemendi väljund on järgmise elemendi sisendiks. Konveierid on arvutites kasutusel selleks, et protsessoril oleks võimalik teha mitu ülesannet ühe takti jooksul. Olenevalt ülesandest võib see drastiliselt suurendada käskude täitmise kiirust. Kui aga on tegu üksteistele järgnevate käskudega, mis kõik omaette olenevad endast varasema käsu tulemusest, siis ei pruugi muutus olla märgatav.

Käsu töötlemise saab jagada näiteks viieks etapiks:

- käsu lugemine (IF)

- käsu dekodeerimine (ID)

- käsu täitmine (EX)

- mälu poole pöördumine (MEM)

- tulemuste salvestamine (WB)

Superskalaarne arhitektuur

[muuda | muuda lähteteksti]Superskalaarseks arhitektuuriks nimetatakse arhitektuuri, mis on varustatud rohkem kui ühe konveieriga. Sellisel korral peavad igal konveieril olema oma komponentide komplekt. Superskalaarse arhitektuuriga seadmetel on kahte tüüpi rakendustega konveiereid:

- sõltumatud konveierid, iga funktsionaalne seade kuulub mingi kindla konveieri juurde

- osaliselt kattuvad konveierid, funktsionaalsete seadmete osas kulude kokkuhoidmiseks on mõned seadmed eri konveierite jaoks ühised.

Vahemälu

[muuda | muuda lähteteksti] Pikemalt artiklis Vahemälu

Pikemalt artiklis Vahemälu

Vahemälu (cache) on suure kiirusega mälu, mis asub protsessorile võimalikult lähedal, kõige kiirem L1-vahemälu asub protsessori põhi räni peal. Vahemälu eesmärk on hoida andmeid mida võib korduvalt vaja minna ning vältida ajakulukat põhimälust andmete leidmist.

Vahemälu tasemed:

- L1-vahemälu

- L2-vahemälu

- L3-vahemälu

- L4-vahemälu (väga harval juhul)

Igal füüsilisel tuumal võib olla mitu käsumootorit (execution unit) ja oma vahemälu. L2- ja L3-vahemälu korral on tihti tegu tuumade vahel jagatud vahemäluga. Kui vahemälu kasutaja (CPU, veebibrauser, operatsioonisüsteem) soovib andmeid, uuritakse kõigepealt vahemälu.

Kui vahemälust leitakse kirje ID-ga, mis sobib otsitud andmeühiku ID-ga, siis kasutatakse andmeelementide vahemälu. Vastasel korral prab pöörduma põhimälu poole.

Käsustik

[muuda | muuda lähteteksti] Pikemalt artiklites Käsustik ja en:Instruction set architecture

Pikemalt artiklites Käsustik ja en:Instruction set architecture

Käsustiku valik võib drastiliselt mõjutada protsessori mikroarhitektuuri kompleksust. CISC protsessori mikroarhitektuur on palju keerulisem, kui RISC protsessoritel, sest neil on aja jooksul kujunenud keerulisemad käsud spetsialiseeritud ülessanete jaoks. RISC protsessorite põhi disaini strateegia oli lihtsustada individuaalseid juhiseid ja nende täitmiseks vajaliku loogikat.

Spekulatiivne käivitamine ja Siirete ennustamine

[muuda | muuda lähteteksti] Pikemalt artiklites en:Speculative execution ja Siirete ennustamine

Pikemalt artiklites en:Speculative execution ja Siirete ennustamine

Siirete ennustamine on tehtud protsessori poolt, et määrata kuhu käskude täitmine läheb peale tingimuslikku hüppet, selleks, et lugeda mälust järgmisi käske. Spekulatiivne käivitamine on 1 samma rohkem ja tegelikult määrab mis järgneva koodi tulemus oleks.

Spekulatiivse käivitamise puhul käivitatakse kood enne kui selle koodi tulemusi vaja läheb teadmata kas selle koodi tulemust läheb vaja. See tähendab, et tingimusliku hargnemise puhul käiakse läbi mõlemad harud ja kui selgub kummale poole kood tegelikult peale minema peab siis heidetakse vale haru ära. Seda on võimalik teha kui protsessoril on vabu ressursse. Kaasaegsetel protsessoritel võimaldab see meetod paremini ära kasutada konveiereid ja konveieri registrites olevaid ressursse.

Siirete ennustamine on programmis olevate hüpete ennustamine enne, kui on teada kas hüpe sooritatakse. Kuna instruktsioonide konveier on mitmesammuline ja käsu täitmiseks kulub mitu takti, siis hüppele järgnevaid käske ei saa alati kohe mällu laadida, vaid tuleb oodata, kuni eelnevad käsud on konveieri läbinud ja nende tulemuse järgi on teada, kas hüpe toimub. Siirete ennustamise võimaluse puudumisel peab protsessor ootama ära hüppe sooritamiseks vajaliku tingimuse tulemust.

Ennustamise implementeerimise viisid:

- Staatiline ennustamine, ennustatakse, et alati tuleb tingimus kas tõene või väärne.

- Küllastuv loendur, iga kord kui on välja arvutatud, kas hüpe toimub või mitte, uuendatakse loenduri olekut. Kui hüpe ei toimunud, siis muudetakse olekut selliselt, et hüppe toimumise tõenäosus on ühe astme võrra madalam. Vastasel juhul tõstetakse tõenäosust ühe astme võrra kõrgemale.

- Kahetasemeline adaptiivne ennustamine, koodis olevate hüpete toimumises võib esineda mustreid. Sellistes olukordades töötab kahetasemeline ennustamine paremini kui küllastuv loendur. Kahetasemeline adaptiivne ennustaja peab meeles viimase n hüppe ajalugu ja kasutab iga 2n ajaloo variandi jaoks küllastuvat loendurit.

- Lokaalne siirete ennustamine, kus igal hüppel on eraldi enda ajaloo puhver. Võidakse kasutada kahetasemelist adaptiivset ennustamist või muud ennustamist.

- Globaalne siirete ennustamine, selle korral ei hoita iga hüppe jaoks eraldi andmeid, vaid kõigil hüpetel on ühine ajalugu. Antud meetodi efektiivsuse jaoks on vajalik suur tabel ajaloo hoidmiseks. Kahetasemelise adaptiivse ennustaja korral kasvab ajalugude tabel eksponentsiaalselt meeles hoitavate hüpete arvust.

- Hübriidne ennustamine, mille korral kasutatakse mitut ennustamismeetodit. Lõpp otsust tehes arvestatakse meetodite individuaalseid täpsusi.

- Tsüklite ennustamine, tsüklis olevaid hüppeid on kõige parem ennustada spetsiaalse ennustajaga. Tsüklite ennustamine on osa hübriidsest süsteemist, kus vastavalt sellele, kas tuvastatakse tsüklilist käitumist, võetakse tsükli ennustaja või mõne muu ennustaja otsust kuulda.

- Masinõppel põhinev ennustamine, masinõppe mudeleid kasutades on võimalik saada paremaid tulemusi kui hübriid ennustuse korral. Masinõppe ennustusel on võimalik kasutada pikka ajalugu, kuid selle optimeerimiseks võib kuluda palju protsessoritsükleid.

Dünaamiline ajastamine

[muuda | muuda lähteteksti] Pikemalt artiklis en:Out-of-order execution

Pikemalt artiklis en:Out-of-order execution

Dünaamiline ajastamise[6] (dynamic execution või out-of-order execution) puhul käivitatakse koodi võimalusel erinevas järjekorras, et optimeerida konveieri kasutust ja minimseerida seisakuid. Näiteks kui protsessor peab ootama, et mingit informatsiooni põhimäust leitakse, siis on ootamise ajal võimalik täita teise käske mis ei vaja andmeid mälust.

Multitöötlus, mitmeprotsessorilisus ja mitmelõimelisus

[muuda | muuda lähteteksti] Pikemalt artiklites en:Multiprocessing , en:Multithreading ja en:Multiprocessor system architecture

Pikemalt artiklites en:Multiprocessing , en:Multithreading ja en:Multiprocessor system architecture

Multitöötlus (multiprocessing) on mitme protsessori kasutus ühe arvuti süsteemi sees. Multitöötlussüsteemis võivad kõik protsessorid olla võrdsed, tuntud kui sümmeetriline multitöötlus, või võib tegu olla süsteemiga kus on üks põhiprotsessor mis jagab ülesandeid teistele protsessoritele, asünkroonne multitöötlus. Multitöötluse all mõeldakse pigem, et ühe füüsilise protsessori kiibi sees on mitu n.ö loogilist protsessorit.

Mitmeprotsessorilisus[7] (multiprocessor system) on kui ühe süsteemi sees on mitu füüsilist protsessorit.

Mitme protsessoriga süsteemide tüübid:

- Leebelt ühendatud mitmeprotsessorisüsteem (loosely coupled multiprocessor system), igal protsessoril on oma mälu, sisend väljund ja operatsioonisüsteem

- Rangelt ühendatud mitmeprotsessorisüsteem (tightly coupled multiprocessor system), protsessorite vahel on jagatud mälu, kõik protsessorid on homogeensed ja ühe operatsioonisüsteemi all.

- Homogeenne mitmeprotsessorisüsteem (homogeneous multiprocessor system), kõik protsessorid mis süsteemis on peavad olema sama protsessor, näiteks peavad kõik kolm süsteemi protsessorid olema i9 9900k protsessorid.

- Heterogeenne mitmeprotsessorisüsteem (heterogeneous multiprocessor system), süsteemis olevad protsessorid, sealhulgas graafikaprotsessorid ja muud teised spetsialiseeritud ülesandega protsessorid, on käik ühendatud sama siiniga ning on võimelised töötama samal tasemel mis põhi protsessor.

- Jagatud põhimäluga mitmeprotsessorisüsteem (shared memory multiprocessor system), protsessorite vahel on jagatud mälu

- Jaotatud põhimäluga mitmeprotsessorisüsteem (distributed memory multiprocessor system), igal protsessoril on oma põhimälu, tavaliselt on see mälu sellele protsessorile nii lähedal kui võimalik.

- Ühtse mälu juurdepääsuga (UMA) süsteem (uniform memory access system)

- Vahemälu sidumisega ebaühtlase põhimälu juurdepääsuga süsteem (cc–NUMA system ehk Cache-coherent non-uniform memory access system), igale protsessorile on globaalsest mälust n.ö partitsioneeritud mingi osa kasutamiseks,

- Hübriidsüsteem (hybrid system), kus lokaalsete andmete jaoks on lokaalne süsteemi mälu ja globaalsete jaoks on olemas globaalne mälu.

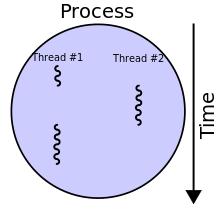

Mitmelõimelisus (multithreading) on protsessori või protsessori tuuma võime jagada programm mitmele lõimele laiali.

See on erinev multitöötlusest, sest mitmelõimelises programmis lõimed jagavad ühe või mitme tuuma ressursse, sealhulgas vahemälu, puhvreid jm. Kui multitöötlussüsteemid sisaldavad mitmeid töötlusplokke ühes või mitmes tuumas, siis mitmelõimelisuse eesmärk on optimeerida ühe tuuma kasutust.

Viited

[muuda | muuda lähteteksti]- ↑ Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering (PDF). Association for Computing Machinery. 2004. Lk 60. Originaali (PDF) arhiivikoopia seisuga 3. juuli 2017.

- ↑ Hennessy, John L.; Patterson, David A. (2006). Computer Architecture: A Quantitative Approach (4th ed.). Morgan Kaufmann. ISBN 0-12-370490-1.

- ↑ Flynn, Michael J. (2007). "An Introduction to Architecture and Machines". Computer Architecture Pipelined and Parallel Processor Design. Jones and Bartlett. Lk 1–3. ISBN 9780867202045.

- ↑ Murdocca, Miles; Heuring, Vincent (2007). Computer Architecture and Organization, An Integrated Approach. Wiley. Lk 151. ISBN 9780471733881.

- ↑ Clements, Alan. Principles of Computer Hardware (4th ed.). Lk 1–2.

- ↑ "Käsukonveierid, käsutaseme paralleelsus, dünaamiline ajastamine ja spekulatiivne käivitamine EUCIP".

- ↑ "Multiprocessor definition and meaning - Collins English Dictionary". www.collinsdictionary.com.

Lisalugemist

[muuda | muuda lähteteksti]- Hamacher, C.; Vranesic, Z.; Zaky, S.; Manjikian, N. (2012). Computer Organization and Embedded Systems 6th edition. McGraw-Hill. ISBN 9780071089005.

- Ledin, Jim (2020). Modern Computer Architecture and Organization. Pact Publishing. ISBN 978-1-83898-439-7.

- Zhirkov, Igor (2017). Low-Level Programming (C, Assembly and Program Execution on Intel 64 Architecture). Aperss. ISBN 9781484224021.